PIC(Peripheral Interface Controller)は、マイクロチップ社によって開発されたマイクロコントローラー(マイコン)です。

PICマイコンのアーキテクチャはハーバード・アーキテクチャに基づいており、高速実行、プログラミングの容易さ、幅広い入手可能性、他の周辺機器とのインターフェースの容易さ、低コスト、フラッシュ・メモリによる再プログラミングなどにより、非常に人気がありるマイコンです。

PIC16F84Aの概要

1998年にマイクロチップ社から発表されたPIC16F84Aは、初心者向けマイコンとしても知られおり、高性能RISC CPUを搭載しています。

詳細はマイクロチップ社が提供しているPIC16F84AData Sheetを参照してください。

- データ・バスのサイズは8ビットの8ビットマイコンです

- 35個のアセンブリ言語命令しかないため、PICマイコンのプログラミング学習に適しています。

- 命令は14ビット(1ワード)で構成され、分岐命令を除き、すべての命令は1サイクルで完了します。

- 命令を格納するプログラム・メモリの容量は1024ワード(1ワードは14ビット)です。

- 最大動作周波数は20MHですが、電力を節約するために低い周波数でも動作させることができます。

- 各ピンに流れ込む(シンク)電流と、流れ出る(ソース)電流の最大値は25mAです。

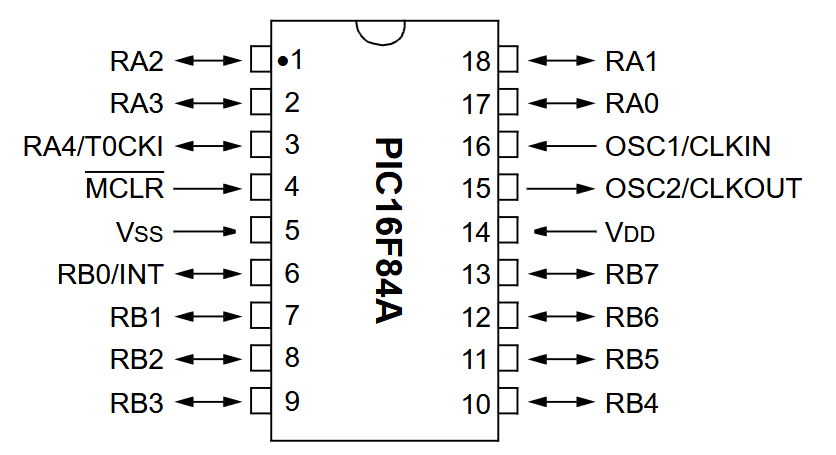

ピン配置

13本あるGPIOピンはPORTA(RA0-RA4の5ピン)とPORTB(RB0-RB7の8ピン)に分けられており、各ピンはデジタル入力またはデジタル出力として使用できます。

| ピンNo | 名 称 | 説 明 |

| 1 | RA2 | 双方向 I/O ポート(ポートAのビット2) |

| 2 | RA3 | 双方向 I/O ポート(ポートAのビット3) |

| 3 | RA4/T0CKI | 双方向 I/O ポート(ポートAのビット4)、 タイマクロック入力 |

| 4 | MCLR | マスター・クリア ( リセット ) 入力、 通常はHightレベルに接続 |

| 5 | VSS | 電源(GNDに接続) |

| 6 | RB0/INT | 双方向 I/O ポート(ポートBのビット0)、 外部割込み |

| 7 | RB1 | 双方向 I/O ポート(ポートBのビット1) |

| 8 | RB2 | 双方向 I/O ポート(ポートBのビット2) |

| 9 | RB3 | 双方向 I/O ポート(ポートBのビット3) |

| 10 | RB4 | 双方向 I/O ポート(ポートBのビット4) |

| 11 | RB5 | 双方向 I/O ポート(ポートBのビット5) |

| 12 | RB6 | 双方向 I/O ポート(ポートBのビット6) |

| 13 | RB7 | 双方向 I/O ポート(ポートBのビット7) |

| 14 | VDD | 電源(+5Vに接続) |

| 15 | OSC2/CLKOUT | オシレータ、セラミック発振子などを接続 |

| 16 | OSC1/CLKIN | オシレータ、セラミック発振子などを接続 |

| 17 | RA0 | 双方向 I/O ポート(ポートAのビット0) |

| 18 | RA1 | 双方向 I/O ポート(ポートAのビット1) |

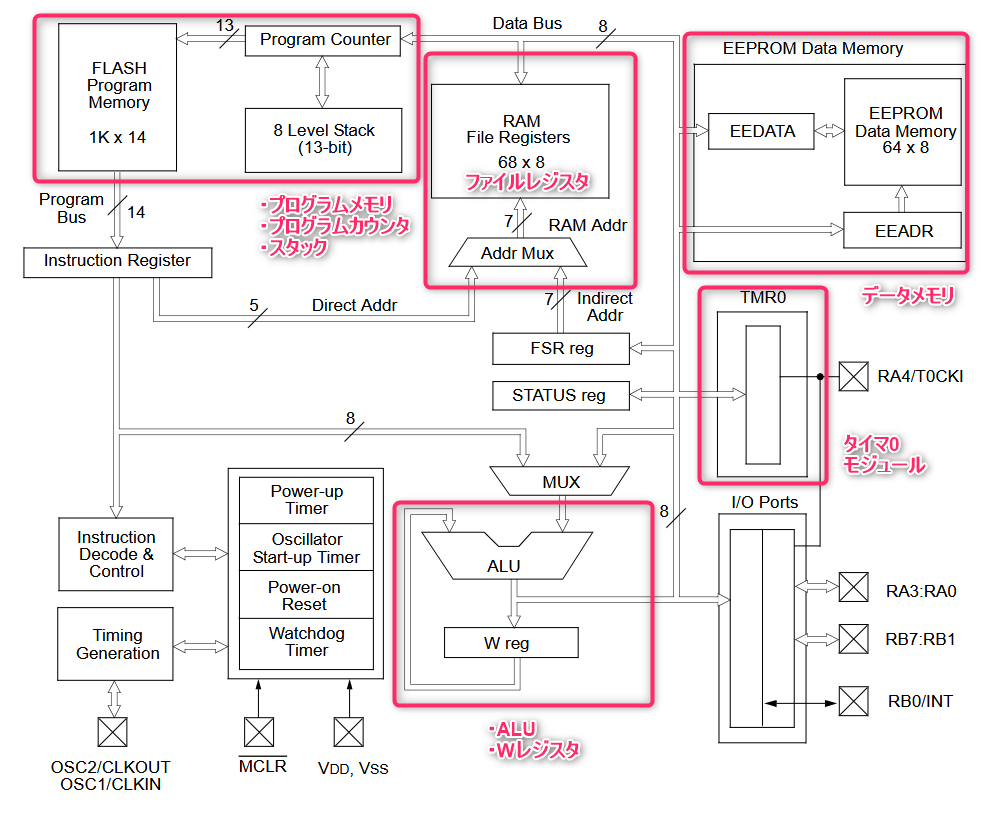

構成

PIC16F84Aは下図の構成になっています。

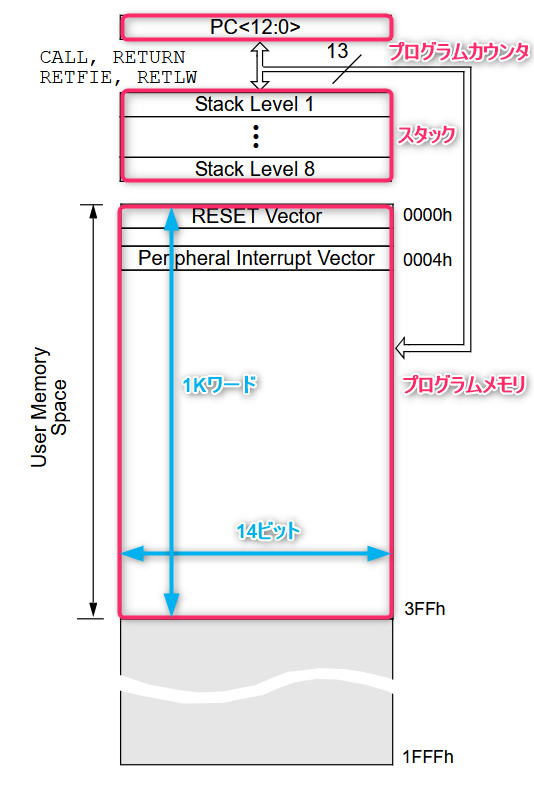

プログラムメモリ/プログラムカウンタ/スタック

プログラムメモリ(FLASH ROM)はプログラムを格納するメモリで、命令は14ビット(1ワード)で表現され、PIC16H84Aでは1024(1K)個の命令を保存することができます。

プログラムメモリ(FLASH ROM)への書き込みは、ROMライタを使って行います。

- 先頭のアドレスは0000h番地で最終アドレス03FFh番地です。(末尾ににhを付けて16進数を表記します。)

- プログラムメモリのアドレスはプログラムカウンタ(PC)で指定され、内容を読み込み(フェッチ)命令が実行されます。

- 電源投入時やMCLRピンによるリセットが発生した場合、プログラムはプログラムメモリの0000h番地に入っている命令を実行します。

- 割込みが発生した場合は、プログラムメモリの0004h番地に入っている命令を実行します。

- プログラムカウンタ(PC)は13ビット長(1FFFh)であるため、最大8192(8K)ワードのプログラムメモリのアドレス指定ができため、PIC16F84Aより多くのプログラムメモリを持っているPICにも適用できます。

但し、GOTOやCALLなどのジャンプ命令の場合は、命令で指定できるアドレスは最大11ビット(2048=2K)であるため、それ以上のアドレスを指定するため、8Kワードの領域を4ページに分割し、ページを切り替えることで、最大8Kワードのプログラムメモリを利用することができます。

PIC16F84Aは最大1Kワードのプログラムメモリを指定しますで、ペーという考え方は必要ありません。 - GOTOやCALLなどのジャンプ命令を除き、命令実行後はプログラムカウンタ(PC)が+1され、次のアドレスの命令がフェチされ実行されます。

GOTOやCALLなどのジャンプ命令の場合は、命令で指定されたアドレスがプログラムカウンタ(PC)に設定され、該当するアドレスのプログラムメモリの内容がフェッチされ実行されます。 - スタックは CALL命令を実行してサブルーチンを呼び出し、サブルーチンの処理が終了した後に復帰するアドレスを保持するために使用されます。

8領域が用意されていることから、サブルーチンにネストは8回までとなります。

ALU/Wレジスタ

ALU(Arithmetic Logic Unit) は 8 ビット幅で、加算、減算、シフトと論理演算を行うことができます。

Wレジスタ(Working Register)は ALU の実行に使用される 8 ビットのレジスタで、演算や転送命令を実行するときに、データを一時的に保管しておきます。

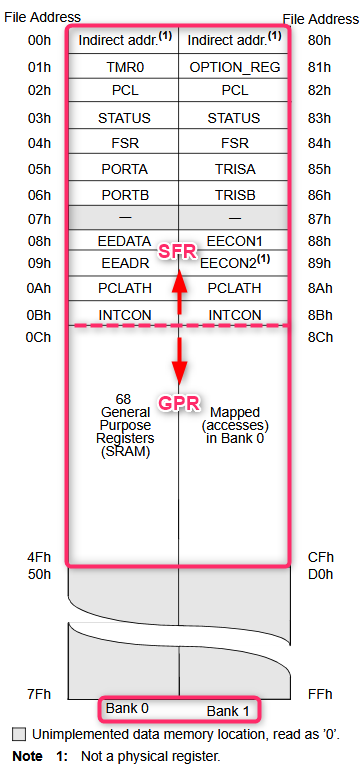

ファイルレジスタ

ファイルレジスタは、8ビットのデータを格納する高速なメモリで、「Addr Mux」から出力される7ビットのアドレスバスでアドレスが指定されます。

RAMが使われているため、電源を切ると記憶した内容は消失します。

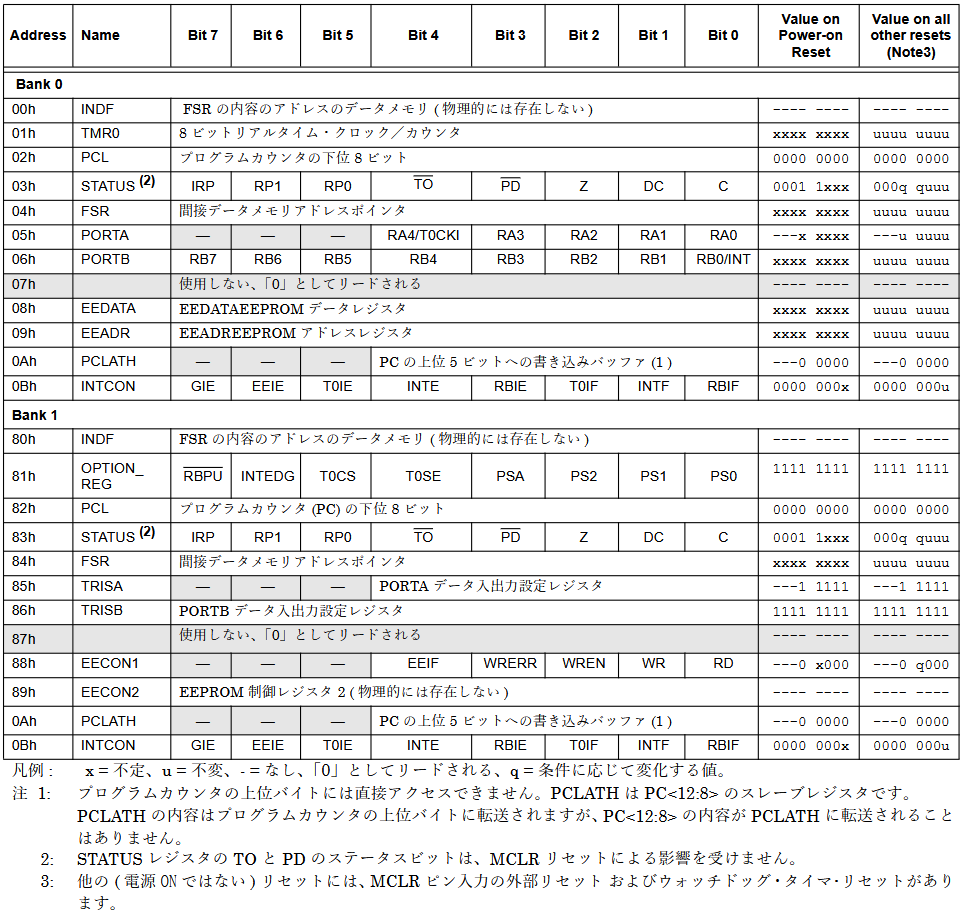

7ビットのアドレス(0番地~7Fh番地)で指定される128領域の内、上位0番地~0Bh番地までの12領域は、SFR(Special Function Registers)と呼ばれる特殊な機能を持ったレジスタに割り当てられており、残りの領域がGPR(General Purpose Registers)と呼ばれるユーザが使用する汎用レジスタです。

PIC16F84Aは0番地~4Fh番地で指定される80領域が実装されているため、汎用レジスタは0C番地~4Fh番地までの68領域になります。

ファイルレジスタは4つのバンクを切り替えることで、最大128X4=512領域を扱うことができます。

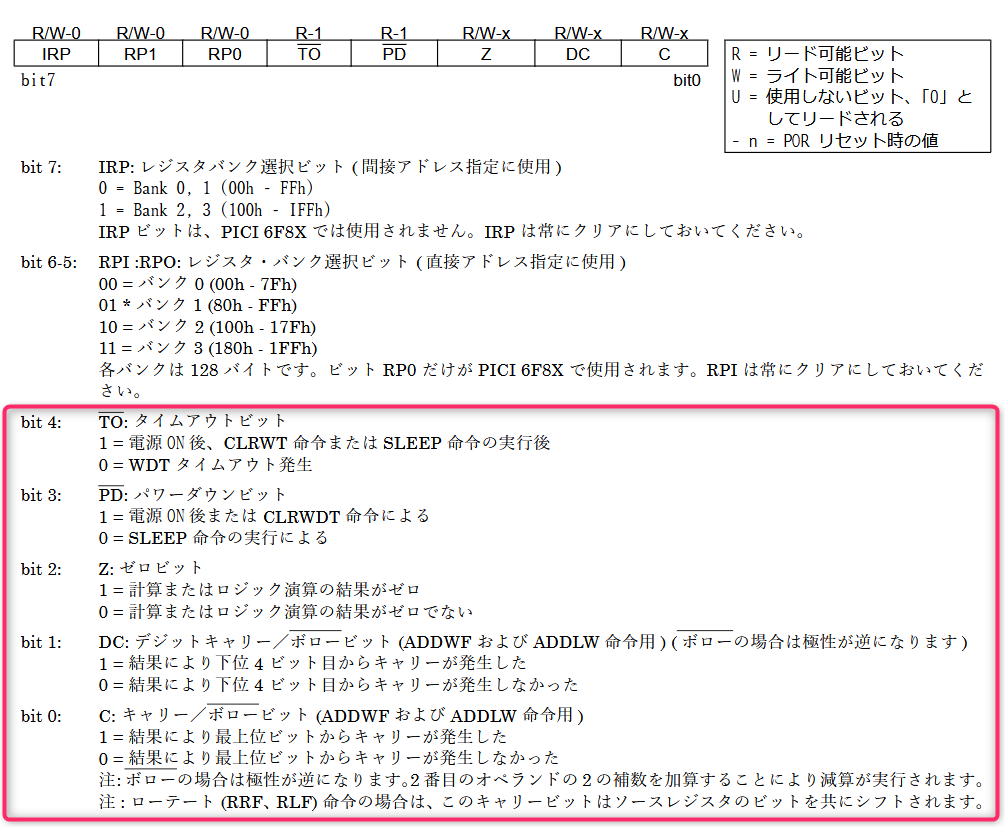

PIC16F84Aのファイルレジスタは4つの内、2つのバンク(Bank0、Bank1)を持っており、SFRの中にあるSTATUSレジスタのRP0(ビット5)を0と1に設定することで、それぞれバンク0とバンク1に切り替えることができ、バンク0では0番地~4Fh番地、バンク1では80h番地~CFh番地が有効なアドレスとなります。

バンク0とバンク1で同じ名前のSFRについては、バンク0を参照することになり、GPRについてはバンク 1 の GPR アドレスは、バンク 0 のアドレスにマップされます。例えば、アドレス番地 0Ch と 8Chは、同一の GPR にアクセスします。

SFR(特殊機能レジスタ)

SFRはファイルレジスタの0番地~0Bh番地(バンク0)と80h番地~8Bh番地(バンク1)に割り当てられており、PICの各種設定などを行う重要な働きをします。

例えば、RB1(7番ピン)の出力をHighに設定する手順(概要)は次のようになります。

- RB1は双方向 I/O ポートですので、出力方向として設定します。

・SFRの86h番地のTRSBレジスタ(PORTBのデータ方向設定レジスタ)のRB1に対応するビットを、出力方向(1)に設定します。 - RB1の出力をHighに設定します。

・SFRの06h番地のPORTBレジスタのRB1に対応するビットをHigh(1)に設定します。

汎用レジスタのアドレス指定方式

汎用レジスタ(GPR)にアクセスする方法として、アドレスを直接してする方法(直接アドレッシング)と間接的に指定する方法(間接アドレッシング)があります。

直接アドレッシングはアドレスを直接指定して、汎用レジスタをアクセスしますが、間接アドレッシングはSFRの00h番地のINDFレジスタと04番地のFSRレジスタをとおして、汎用レジスタをアクセスします。

- ファイルレジスタのバンクはSTATUSレジスタのIRP(ビット7)と、FSRレジスタの最上位ビット(ビット7)によって選択されますが、PIC16F84Aのバンクは2個ですので、IRPは常に0に設定され、FSRレジスタの最上位ビットだけで選択します。

- 汎用レジスタの内容を取り出す場合は、FSRレジスタの下位7ビットに汎用レジスタのアドレス書込んだ後、INDFレジスタを読み取ります。

- 汎用レジスタにデータを書き込む場合は、FSRレジスタの下位7ビットに汎用レジスタのアドレス書込んだ後、書き込むデータをINDFレジスタに書き込みます。

データメモリ

データメモリ(EEPROM)は、書込みに10msほどかかるため、通常のプログラムで処理するデータ格納には書込み時間が早い汎用レジスタを使います。

データメモリ(EEPROM)はプログラムメモリ(FLASH ROM)と同様に、電源を切ってもデータが消えないため、重要なデータを格納する目的で使われます。

プログラムメモリ(FLASH ROM)への書き込みは、ROMライタを使って行いますが、データメモリ(EEPROM)への書込みはROMライタは必要ありません。

通常プログラムで使うMOV命令等では、書込みを直接行うことができませんので、SFRにあるEEADRレジスタ(09h番地)、EEDATAレジスタ(08h番地)、EECON1レジスタ(88h番地)、EECON2レジスタ(89h番地)を使って行います。

読出しはEEADRレジスタ(09h番地)、EEDATAレジスタ(08h番地)、EECON1レジスタ(88h番地)を使って行います。

タイマ0モジュール

タイマ0モジュールは8ビットのアップカウンタで、FFh から 00h にオーバーフロー(256を超えた)したとき、TMR0 割り込みが発生し、INTCONレジスタ(8Bh)のT0IF(ビット2)が1になります。

割り込みが発生するとプログラムカウンターはハードにより強制的に0004hになり、そこからプログラムが走り始めます。割り込みを発生させるためにはINTCONレジスタ(8Bh)のGIE(ビット7)およびT0IE(ビット5)を1に設定します。

8ビット(256)ではカウントが足りない場合は、入力を8段階(2、4、8、16、32、64、128、256)に分周する分周器が備わっているため、最大256x256=65536を超えたとき、TMR0 割り込みを発生させることができます。

分周器の設定はSFRの81番地のOPTION_REGレジスタの(ビット0~ビット2)で設定します。

SFRの81番地のOPTION_REGレジスタのTOS(ビット5)を0に設定すると、システムクロックでカウントされ、1に設定するとRP4/TOCK1(3番ピン)から入力される信号でカウントされます。

PIC16F84Aは一つの命令は4クロックで動作することが基本になっていますので、入力信号として20MHzのシステムクロックを使う場合は、カウンタには20MHz/4=5MHzが入力されます。

分周器を使わない場合(256)、タイマ0がオーバーフローする時間は1/5MHz X 256 =51.2μsecになり、分周器を256に設定した場合、タイマ0がオーバーフローする時間は1/5MHz X 256 X 256 =13107.2μsec(約13ms)になります。

ウオッチドッグタイマ(WDT)

ウオッチドッグタイマ(WDT)は、プログラムに暴走を監視し、暴走していた場合はシステムをリセットします。

リセットは設定したタイマのカウントが終了した場合に発生しますので、ウオッチドッグタイマを起動し、カウントが終了する前にウオッチドッグタイマをクリアすることを通常の処理の中で繰返し行います。

ウオッチドッグタイマを動作させる発振器は、PICに内蔵されており、システムクロックとは独立していますので、システムクロックが停止しても動作します。

ウオッチドッグタイマも分周器を使うことができますが、タイマ0モジュールと重複して使うことができません。

また、分周もタイマ0モジュールとは異なり、1,2、4、8、16、32、64、128の8段階です。

ウオッチドッグタイマはコンフィグレーションビットを設定することで、有効、無効にすることができます。

ウオッチドッグタイマをクリアにする場合は、プログラムの中でCLRWDT命令を実行します。

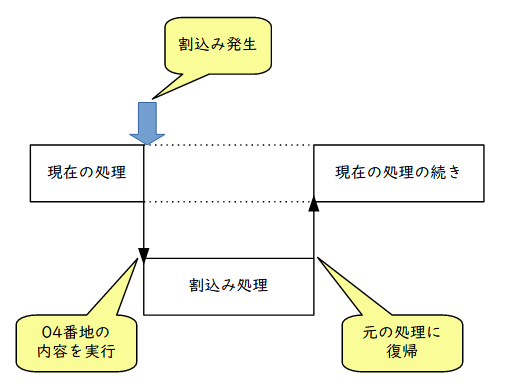

割込み

割込みは、現在実行している処理を停止させ、他の処理に実行を移し処理終了後、停止している処理の次の処理を実行します。

PIC16F84Aの割込みの発生は次の4種類です

- RB0/INT(ポートBのビット0 6番ピン)に入力された信号が立ち上がった時、または立ち下がった時に割込みが発生します。

立上り、立下りはS、FRの81番地のOPTION_REGレジスタのINTEDG(ビット6 0:立上り 1:立下り)で設定します。 - RB4~RB7(ポートBのビット4~7 10番~13番ピン)の入力信号が変化した時に、割込みが発生します。

- タイマ0がオーバーフローした時に、割込みが発生します。

- データメモリ(EEPROM)は書込み時間が長いため、その間の処理を停滞させないように、データの書込みが終了した時に、割込みが発生します。

割込みはSFRの0Bh番地INTCONレジスタで設定します。

| ビット | 名 称 | 説 明 |

| 0 | RBIF | ポートB 割込みフラグビット 1 = 少なくとも 1 つ以上の RB4~RB7 ピンの状態が変化した ( プログラムでクリアする必要があります) 0 = 状態が変化した RB4~RB7 ピンはない |

| 1 | INTF | RB0/INT 割込みフラグビット 1 = RB0/INT 割り込みが発生した (プログラムでクリアする必要があります ) 0 = RB0/INT 割り込みが発生していない |

| 2 | TOIF | タイマ0 割込みフラグビット 1 = タイマ0 がオーバーフローした (プログラムでクリアする必要があります ) 0 = タイマ0 がオーバーフローしていない |

| 3 | RBIE | RB4~RB7 割込みイネーブルビット 1 = RB4~RB7 ポート変化割り込み発生を許可します 0 = RB4~RB7ポート変化割り込み発生を禁止します |

| 4 | INTE | RB0/INT 割込みイネーブルビット 1 = RB0/INT 割り込み発生を許可します 0 = RB0/INT 割り込み発生を禁止します |

| 5 | TOIE | タイマ0 割込みイネーブルビット 1 = タイマ0 割込み発生を許可します 0 = タイマ0 割込み発生を禁止します |

| 6 | EEIE | EEPROM 割込みイネーブルビット 1 = EEPROM 書込み完了割り込み発生を許可します 0 = EEPROM 書込み完了割り込み発生を禁止します |

| 7 | GIE | すべての割込みイネーブルビット 1 = すべてのマスクされていない割り込み発生を許可します 0 = 全ての割り込み発生を禁止します |

- 割込みが発生すると、現在実行中のアドレスがスタックメモリに保存されます。

- プログラムメモリの04番地(割込みベクタ)が実行されます。

- 発生した割込みに該当するフラグビット(TOIF、INTF、RBIF)が1にセットされますので、割込みの処理が終了した後、プログラムでクリアに(0に戻す)する必要があります。

通常プログラムはリセット後、0番地から実行されますので、割込みを使う場合は04番地の実行を避けるようにします。

スリープ

SLEEP 命令を実行すると、スリープ ( パワーダウン ) モードに入り、消費電力が少なくなります。

レジスタやメモリに内容は保持され、クロックは停止しますが、ウオッチドッグタイマは停止しません。

リセット、内部、外部割り込み、ウオッチドッグタイマのタイムアウトにスリープからの目覚めますが、ウオッチドッグタイマのタイムアウトによるスリープからの起動は通常動作の継続され、リセットはされません。

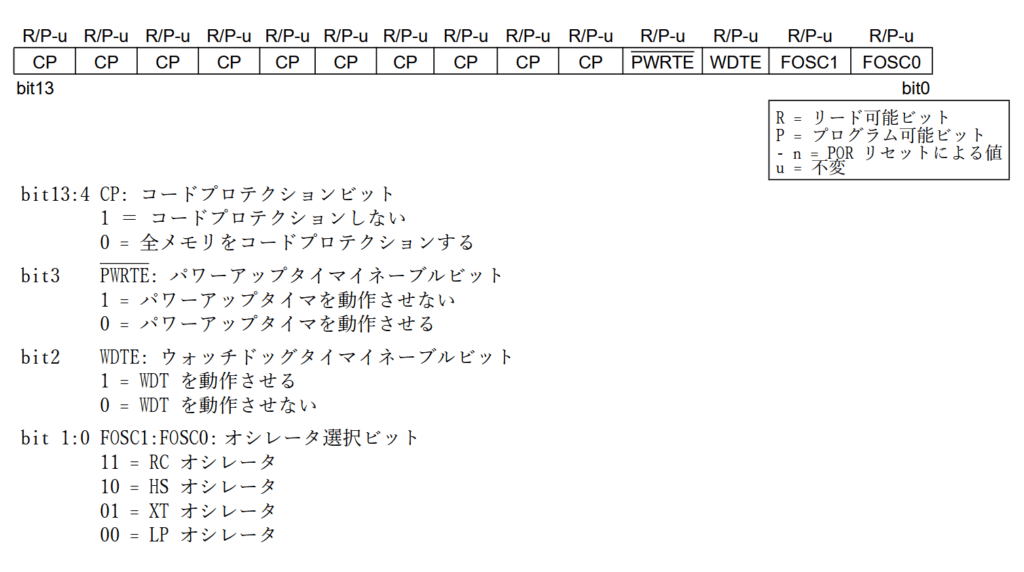

コンフィグレーションビット

コンフィグレーションビットは、PIC16F84Aの特殊機能を設定する14ビット長の領域で、「Configuration Bits Window」で設定し、ア プリケーションに配置するためのコードを生成します。

▶️コンフィグレーションビットの構成

▶️オシレータ(発振)の種類

PIC16F84Aは 4 つのオシレータモードで動作できます。

2 ビットのコンフィグレーションビット (F0SC1 および F0SC0) をプログラムして、以下の 4 種類のモードから 1 つを選択することができます。

XT、LP または HS モードでは、水晶またはセラミックリゾネータを OSC1/CLKIN および OSC2/CLKOUTピンに接続して発振させます。

| モード | 周波数 | 説 明 |

| LP | 40KHz | 低消費電力水晶を使用します |

| XT | 0~10MHz | 水晶/セラミックリゾネータを使用します |

| RS | 4~20MHz | 高速水晶/セラミックリゾネータを使用します |

| RC | 0~4MHz | 抵抗とコンデンサの組わせで発振できますが、タイミング精度が落ちます |

▶️WDTE: ウォッチドッグタイマイネーブルビット

プログラムの暴走を監視する、ウォッチドッグタイマの有効/無効を設定します。

▶️PWRTE: パワーアップタイマイネーブルビット

有効にした場合、電源電圧が動作範囲内に達するまで、停止状態にします。

▶️CP: コードプロテクションビット

無効にした場合、プログラムメモリからプログラムを読みだせなくなります。

アセンブラ言語(MPLAB X IDE v6.20対応)

マイコンは、0と1(2進数表記)の組み合わせで表現される「機械語」の命令で制御されます。

機械語は人間にとっては大変、扱いにくい形式であるため、「ニーモニック」という人間が分かりやすいように付けられた英数字の短い符号を使って、プログラムを作成していきます。

ニーモニックで作成したプログラムを、機械語に変換してから、マイコンに与えるこで実行することができます。

ニーモニックを使ったプログラム言語のことを「アセンブラ言語」と言い、機械語に変換することを「アセンブラ」と言います。

機械語とアセンブラ言語は異なるものですが、通常はどちらもアセンブラ言語を表わす言葉として使われているようです。

アセンブラ言語の書式

アセンブラ言語は、ラベル、オペコード、オペランドで構成されます。

| ラベル | オペコード(ニーモニック) | オペランド |

【例】

LOOP: BCF MEM, 5 // MEM番地の内容のビット4を0でクリア

- ラベルは行の先頭から記述し、コロン(:)で終了します。

- ラベルがない場合は、先頭に1個以上の半角スペースかタブスペースが必要です。

- それぞれの項目は1個以上の半角スペースかタブスペースで区切ります。

- 1行は255文字以下で記述します。

| 名 称 | 例 | 説 明 |

| ラベル | LOOP: | 英文字または、_(アンダーバー)で始まる32文字以内の半角英数字です。 |

| オペコード | BCF | PIC16F84Aの命令(ニーモニック)や疑似命令を記述します。 |

| オペランド | MEM, 5 | 操作するレジスタやビット、定数等を記述します。 NOP命令のようにオペランドがない命令もあります。 |

| コメント | MEM番地の内容のビット4を0でクリア | 「//」に続く文字、文字列は全て注釈とされ、プログラムの実行には関係ありません。 「/* */」で囲まれた文は全て注釈とされ、プログラムの実行には関係ありません。 |

命令の実行

命令は、プログラムカウンタ(PC)が指定するプログラムメモリのアドレスから命令コードを読み込み(フェッチ)、命令コードを解読し(デコード)、命令実行の3ステップで処理されます

それぞれのステップはクロック(システムクロック)を基準に処理され、フェッチで4クロック、デコード+実行で4クロックの合計8クロックを必要とします。

4クロックを1サイクルと考えるため、ノイマン型マイコンの処理では、フェッチ、デコード、実行の処理は2サイクル必要となります。

PIC16F84Aはハーバード型のマイコンであるため、パイプライン方式を利用することで、デコード+実行と同時に、次の命令のフェッチを行うため、見かけ上、1つの命令を1サイクル(4クロック)で処理することができます。

但し、ジャンプ命令の場合はジャンプ先の命令をフェッチする必要があるので、2サイクル(8クロック)が必要となります。

プログラムカウンタ(PC)は、次に実行する命令のアドレスを格納しておく13ビットのレジスタで、上位5ビットはSFRの02h番地のPCLレジスタ、下位8ビットは0Ah番地のPCLATHレジスタで構成されています。

命令の分類

PIC16F84Aは35個の命令(ニーモニック)の他に、疑似命令と呼ばれるアセンブラを制御する命令が備わっています。

疑似命令は、PICの命令では無く、アセンブラに対する命令で、アセンブラの起動時だけに実行され、機械語には変換されません。

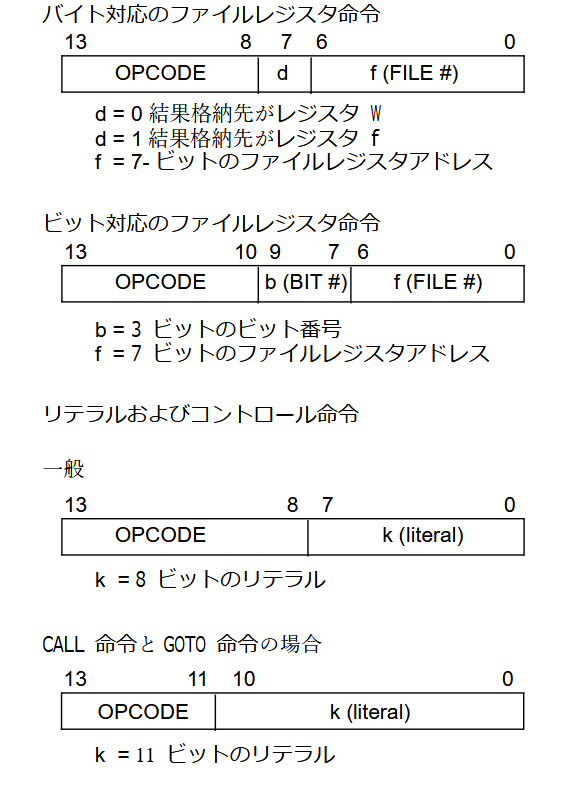

命令はすべて14 ビット(1ワード)で、命令のタイプを表すオペコード部と、その他の命令の動作を表す1つ以上のオペランド部からできており、オペコード部は3~6ビット、ペランド部は8~11ビットとなっています。

命令は、「バイト対応命令」、「ビット対応命令」、「リテラルおよびコントロール命令」に分類できます。

- バイト対応命令では、「f」をファイル レジスタのアドレス、「d」を結果の格納場所として使用します。

「d」が 0 の場合、結果は W レジスタに格納され、「d」が 1 の場合、結果は命令で指定されたファイルレジスタに格納されます。 - ビット対応命令では、「f」 を使ってファイル レジスタのアドレスを指定し、「b」を使って、「f」で指定したファイル レジスタの内容のビットの番号を選択、操作します。

- リテラルおよびコントロール命令では、「k」を使って8 ビットまたは 11 ビットの定数やリテラルを指定します。

▶️PIC16F84Aの命令(35種)の分類

| 分 類 | 命 令 | |

| バイト対応命令 | 転送 | MOVF、MOVWF、SWAPF |

| 算術演算 | ADDWF、SUBWF、INCF、DECF | |

| 論理演算 | ANDWF、IORWF、COMF、XORWF | |

| ローテイト演算 | RRF、RLF | |

| 条件分岐 | INCFSZ、DECFSZ | |

| クリア | CLRF、CLRW | |

| その他 | NOP | |

| ビット対応命令 | ビット操作 | BCF、BSF |

| 条件分岐 | BTFSC、BTFSS | |

| リテラルおよびコントロール命令 | 転送 | MOVLW |

| 算術演算 | ADDLW、SUBLW | |

| 論理演算 | ANDLW、IORLW、XORLW | |

| 無条件分岐 | GOTO | |

| サブルーチン | CALL、RETURN、RETLW、RETFIE | |

| クリア | CLRWDT | |

| 制御 | SLEEP | |

▶️疑似命令

数多くの種類がありますが、大別すると次の6種類です。

| 命 令 | 説 明 |

| LIST命令 | 使用するPICの種類を定義します |

| INCLUDE命令 | 設定ファイルを指定します |

| EQU命令 | 定数をラベル名で定義します |

| END命令 | ソースコードの最後である事を指定します |

▶️命令のフォーマット

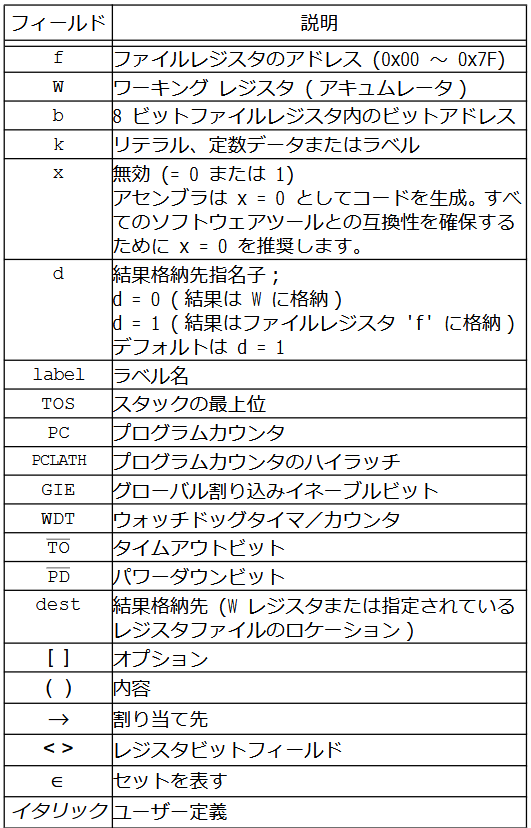

▶️命令の説明に使われている記号

命令の実行で影響を受けるSTATUSレジスタのフラグ

命令によっては、SFRの03h番地のSTATUSレジスタのフラグを表わすビット(Z、DC、C、TO、PD)に影響を与えます。

命令セット

▶️命令の説明に使われている記号(抜粋)

| 記 号 | 説 明 |

| f | ファイルレジスタのアドレス (00h ~ 7Fh) |

| W | ワーキング レジスタ ( アキュムレータ ) |

| b | 8 ビットファイルレジスタ内のビット番号(0 ~ 7) |

| k | 定数データまたは(0 ~ 255) |

| d | 結果格納先を指定 |

| d = 0 ( 結果は W に格納 ) | |

| d = 1 ( 結果はファイルレジスタ 「f」に格納 ) デフォルトは d = 1 | |

| label | ラベル名 |

| [ ] | オプション(省略可能) |

| ( ) | 内容 |

| → | 割り当て先 |

| イタリック | ユーザー定義 |

▶️命令一覧

| No | オペコード | オペランド | 説 明 | 影響 フラグ | サイクル数 |

| バイト対応命令 | |||||

| 1 | MOVF | f, d | ・d=0 ファイルレジスタのf番地の内容をWレジスタに転送します ・d=1 ファイルレジスタのf番地の内容をファイルレジスタf番地に転送します (f番地の内容が0どうか確認) | Z | 1 |

| 2 | MOVWF | f | Wレジスタの内容をァイルレジスタのf番地 | ー | 1 |

| 3 | SWAPF | f, d | ・d=0 ファイルレジスタのf番地の上位4ビットとWレジスタの下位4ビットを入れ替え、結果をWレジスタに格納します ・d=1 ファイルレジスタのf番地の上位4ビットと下位4ビットを入れ替え、結果をファイルレジスタのf番地に格納します | ー | 1 |

| 4 | ADDWF | f, d | ・d=0 Wレジスタの内容とファイルレジスタのf番地の内容を加算し、結果をWレジスタに格納します ・d=1 Wレジスタの内容とファイルレジスタのf番地の内容を加算し、結果をファイルレジスタのf番地に格納します | Z, DC, C | 1 |

| 5 | SUBWF | f, d | ・d=0 ファイルレジスタのf番地の内容からWレジスタの内容を減算し、結果をWレジスタに格納します ・d=1 ファイルレジスタのf番地の内容からWレジスタの内容を減算し、結果をファイルレジスタのf番地に格納します | Z, DC, C | 1 |

| 6 | INCF | f, d | ・d=0 ファイルレジスタのf番地の内容に1を加算(インクレメント)し、結果をWレジスタに格納します(ファイルレジスタのf番地の内容は変化しない) ・d=1 ファイルレジスタのf番地の内容に1を加算(インクレメント)します | Z | 1 |

| 7 | DECF | f, d | ・d=0 ファイルレジスタのf番地の内容から1を減算(デクレメント)し、結果をWレジスタに格納します(ファイルレジスタのf番地の内容は変化しない) ・d=1 ファイルレジスタのf番地の内容から1を減算(デクレメント)する | Z | 1 |

| 8 | ANDWF | f, d | ・d=0 Wレジスタの内容とファイルレジスタのf番地の内容をAND演算し、結果をWレジスタに格納します ・d=1 Wレジスタの内容とファイルレジスタのf番地の内容をAND演算し、結果をファイルレジスタのf番地に格納します | Z | 1 |

| 9 | IORWF | f, d | ・d=0 Wレジスタの内容とファイルレジスタのf番地の内容をOR演算し、結果をWレジスタに格納します ・d=1 Wレジスタの内容とファイルレジスタのf番地の内容をOR演算し、結果をファイルレジスタのf番地に格納します | Z | 1 |

| 10 | COMF | f, d | ・d=0 ファイルレジスタのf番地の内容をNOT演算し、結果をWレジスタに格納します ・d=1 ファイルレジスタのf番地の内容をNOT演算します | Z | 1 |

| 11 | XORWF | f, d | ・d=0 Wレジスタの内容とファイルレジスタのf番地の内容をEX-OR演算し、結果をWレジスタに格納します ・d=1 Wレジスタの内容とファイルレジスタのf番地の内容をEX-OR演算し、結果をファイルレジスタのf番地に格納します | Z | 1 |

| 12 | RRF | f, d | ・d=0 ファイルレジスタのf番地の内容をキャリーフラグを含めて1ビット右に回転させ、結果をWレジスタに格納します ・d=1 ファイルレジスタのf番地の内容をキャリーフラグを含めて1ビット右に回転させ、結果をファイルレジスタのf番地に格納します | C | 1 |

| 13 | RLF | f, d | ・d=0 ファイルレジスタのf番地の内容をキャリーフラグを含めて1ビット左に回転させ、結果をWレジスタに格納します ・d=1 ファイルレジスタのf番地の内容をキャリーフラグを含めて1ビット左に回転させ、結果をファイルレジスタのf番地に格納します | C | 1 |

| 14 | INCFSZ | f, d | ・d=0 ファイルレジスタのf番地の内容に1を加算(インクレメント)し、結果をWレジスタに格納します 結果が0の場合は次の命令をスキップし、0以外の場合は次の命令を実行します(ファイルレジスタのf番地の内容は変化しない) ・d=1 ファイルレジスタのf番地の内容に1を加算(インクレメント)します 結果が0の場合は次の命令をスキップし、0以外の場合は次の命令を実行します 【スキップする場合は2サイクルになります】 | ー | 1(2) |

| 15 | DECFSZ | f, d | ・d=0 ファイルレジスタのf番地の内容から1を減算(デクレメント)し、結果をWレジスタに格納します 結果が0の場合は次の命令をスキップし、0以外の場合は次の命令を実行します(ファイルレジスタのf番地の内容は変化しない) ・d=1 ファイルレジスタのf番地の内容から1を減算(デクレメント)します 結果が0の場合は次の命令をスキップし、0以外の場合は次の命令を実行します 【スキップする場合は2サイクルになります】 | ー | 1(2) |

| 16 | CLRF | f | ファイルレジスタのf番地の内容をクリア(00h)にします | Z | 1 |

| 17 | CLRW | ー | Wレジスタのf番地の内容をクリア(00h)にします | Z | 1 |

| 18 | NOP | ー | 何もおこないません | ー | 1 |

| ビット対応命令 | |||||

| 19 | BCF | f, b | ファイルレジスタのf番地のビットbをクリア(0)にします(他のビットは影響されません) | ー | 1 |

| 20 | BSF | f, b | ファイルレジスタのf番地のビットbをセット(1)にします(他のビットは影響されません) | ー | 1 |

| 21 | BTFSC | f, b | ファイルレジスタのf番地のビットbが0の場合は次の命令をスキップし、0以外の場合は次の命令を実行します 【スキップする場合は2サイクルになります】 | ー | 1(2) |

| 22 | BTFSS | f, b | ファイルレジスタのf番地のビットbが1の場合は次の命令をスキップし、0以外の場合は次の命令を実行します 【スキップする場合は2サイクルになります】 | ー | 1(2) |

| リテラルおよびコントロール命令 | |||||

| 23 | MOVLW | k | 8ビットの定数kをWレジスタに転送します | ー | 1 |

| 24 | ADDLW | k | Wレジスタの内容と8ビットの定数kを加算し、結果をWレジスタに格納します | Z, DC, C | 1 |

| 25 | SUBLW | k | 8ビットの定数kからWレジスタの内容を減算し、結果をWレジスタに格納します | Z, DC, C | 1 |

| 26 | ANDLW | k | Wレジスタの内容と8ビットの定数kとをAND演算し、結果をWレジスタに格納します | Z | 1 |

| 27 | IORLW | k | Wレジスタの内容と8ビットの定数kとをOR演算し、結果をWレジスタに格納します | Z | 1 |

| 28 | XORLW | k | Wレジスタの内容と8ビットの定数kとをEX-OR演算し、結果をWレジスタに格納します | Z | 1 |

| 29 | CALL | label | 命令が実行されると復帰するアドレスをスタックに格納します label(または11ビット幅にアドレス)で指定されるプログラムメモリのアドレスにあるサブルーチンをじっこうします 実行後、RETURN、RETLW命令で元のルーチンに復帰します | ー | 2 |

| 30 | GOTO | label | label(または11ビット幅にアドレス)で指定されるプログラムメモリのアドレスに無条件に分岐します | ー | 2 |

| 31 | RETURN | ー | サブルーチンより復帰します | ー | 2 |

| 32 | RETLW | k | 8ビットの定数kをWレジスタに転送し、サブルーチンより復帰します | ー | 2 |

| 33 | RETFIE | ー | 割込み処理から復帰しまう | ー | 2 |

| 34 | CLRWDT | ー | ウオッチドッグタイマ(WDT)の初期化を行います | TO, PD | 1 |

| 35 | SLEEP | ー | 低電力でのスリープ(待機)モードになります。外部からのリセット、割込み、ウオッチドッグタイマ(WDT)のタイムアウトにより復帰します | TO, PD | 1 |